risc-v isa simulator

Worked on this project in a team of 4 during my college course of Computer Architecture and got a bagged of 100%.

Developed a Simulator Program in C++ to convert the Assembly Language input to a Machine Code,

executed using Memory and Register Arrays for storing data and variables.

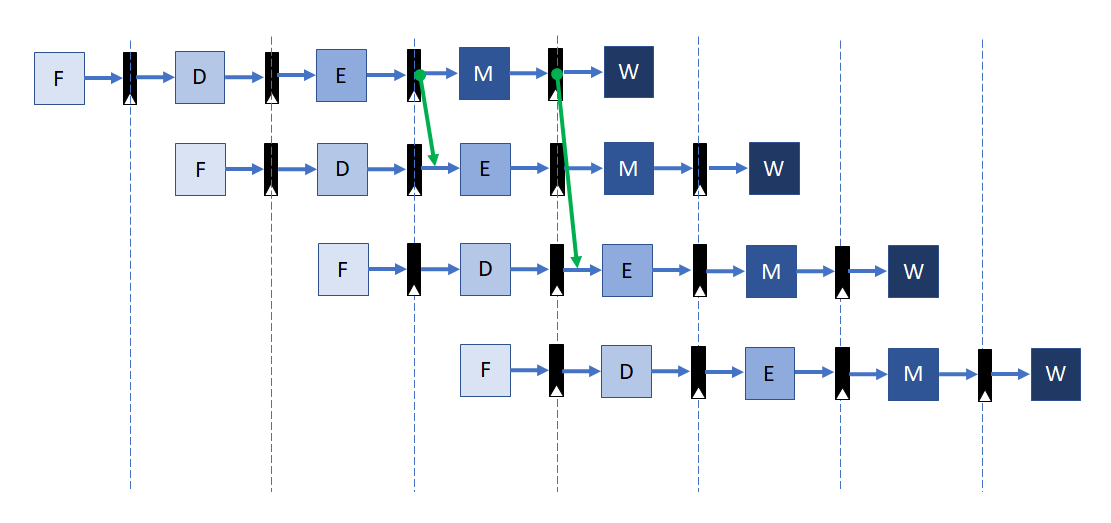

To improve the performance by enabling parallel execution of instructions, the simulator

supports various functionalities including Data Forwarding, Flushing, Pipelining and Branch

Prediction.

Minimized stalling while preventing Data Hazards with the help of Data and Memory Buffers.

Github Link

Pipelining - Buffer Prefetch